# Run-time Spatial Resource Management in Heterogeneous MPSoCs

# **Abstract**

This thesis concerns the arbitration between multiple applications over the resources available in a multi-processor system. Sharing resources can have negative effects on the performance of an application, due to scheduling and inter-task communication. Targetting the domain of streaming applications, many applications require a guaranteed performance for correct behavior. Therefore, we use dataflow models that allow analysis of an application, before it is admitted to the system.

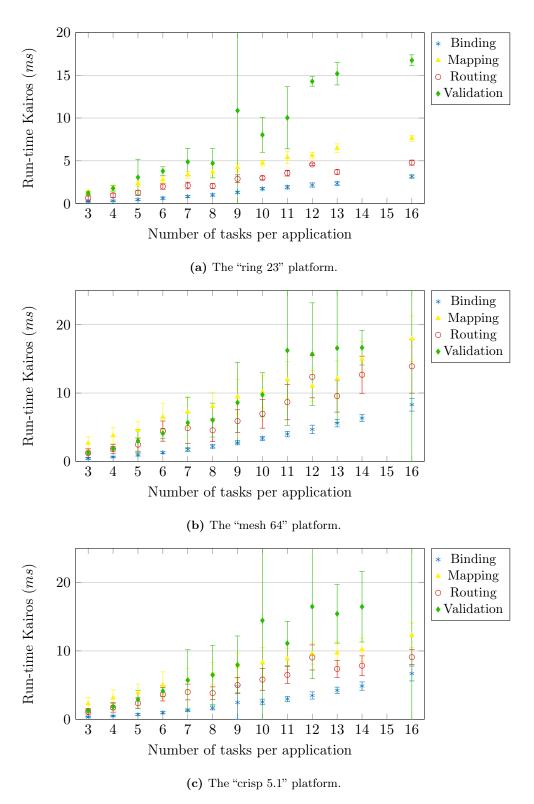

Larger systems introduce a spatial factor into an already complex problem. In this thesis, we propose multiple heuristics to tackle the resource management problem. These heuristics use cost functions to steer the outcome and the optimization direction. Our approach is implemented in a Linux kernel. On lowend ARM processors, a single resource allocation attempt takes tens of milliseconds. Due to the many factors that play a role, we experienced a large variability between admission and failure rates.

Opposed to design-time generated use cases, our approach makes flexible and fault tolerant multi-processor systems available, with a guaranteed performance for critical applications.

# Contents

| Lis | st of | Figures                                     | v  |

|-----|-------|---------------------------------------------|----|

| Lis | st of | Tables                                      | vi |

| 1   | Intr  | oduction                                    | 1  |

|     | 1.1   | Run-time spatial resource management        | 2  |

|     | 1.2   | Research approach and methods               | 3  |

|     | 1.3   | Structure of the thesis                     | 4  |

| 2   | On    | run-time spatial resource management        | 5  |

|     | 2.1   | Design-time preparations                    | 5  |

|     | 2.2   | Assumptions for spatial resource management | 8  |

|     | 2.3   | Taxonomy for spatial resource management    | 10 |

|     | 2.4   | Optimization criteria                       | 21 |

| 3   | Heu   | ristics for spatial resource management     | 23 |

|     | 3.1   | Hardware platforms                          | 23 |

|     | 3.2   | Applications                                | 24 |

|     | 3.3   | The spatial resource management problem     | 25 |

|     | 3.4   | Binding phase                               | 27 |

|     | 3.5   | Mapping phase                               | 29 |

|     | 3.6   | Routing phase                               | 37 |

|     | 3.7   | Execution layout                            | 39 |

| 4   | Con   | straint validation                          | 41 |

|     | 4.1   | Synchronous Data Flow                       | 42 |

|     | 4.2   | Throughput limitations                      | 44 |

|     | 4.3   | Modeling buffering                          | 44 |

|     | 4.4   | Modeling communication latency              | 46 |

|     | 4.5   | Throughput analysis                         | 48 |

|     | 4.6   | Latency analysis                            | 51 |

|     | 4.7   | Improved accuracy with latency-rate servers | 55 |

|     | 4.8   | Validation of the execution layout          | 57 |

iv CONTENTS

| 5            | Imp   | lementation                                      | <b>59</b> |

|--------------|-------|--------------------------------------------------|-----------|

|              | 5.1   | System overview                                  | 59        |

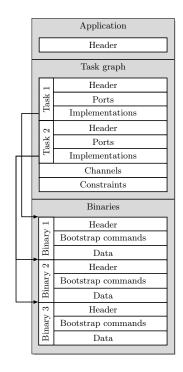

|              | 5.2   | Application specifications as input              | 60        |

|              | 5.3   | Workflow within the Linux kernel                 | 62        |

|              | 5.4   | Execution layouts as output                      | 63        |

|              | 5.5   | Virtual environment                              | 64        |

| 6            | Res   | ults                                             | 67        |

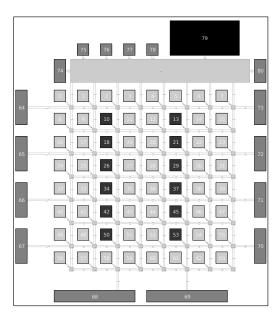

|              | 6.1   | Case study: a 16-channel beamforming application | 67        |

|              | 6.2   | Synthetic benchmark                              | 68        |

|              | 6.3   | Discussion                                       | 70        |

| 7            | Con   | aclusion                                         | 77        |

|              | 7.1   | Recommendations for further research             | 77        |

|              | 7.2   | Acknowledgments                                  | 80        |

| $\mathbf{A}$ | MP    | SoC File Format                                  | 81        |

| $\mathbf{B}$ | Cas   | e study: Beamforming application                 | 87        |

|              | B.1   | Specification                                    | 87        |

|              | B.2   | Resulting execution layout                       | 88        |

| Re           | efere | nces                                             | 91        |

# List of Figures

| 1.1  | Context of run-time spatial resource management             |

|------|-------------------------------------------------------------|

| 2.1  | Design-time exploration of applications                     |

| 2.2  | Task migration                                              |

| 2.3  | Various phases of a resource management algorithm           |

| 2.4  | Example of resource fragmentation                           |

| 2.5  | Cluster-based mapping                                       |

| 2.6  | Incremental application mapping                             |

| 2.7  | The "GuarVC" NoC router                                     |

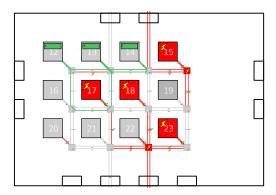

| 3.1  | The spatial resource management problem                     |

| 3.2  | Set representation of iterative mapping                     |

| 3.3  | External fragmentation on some example platforms            |

| 3.4  | Searching elements                                          |

| 3.5  | Example of application mapping                              |

| 3.6  | Multicast routing                                           |

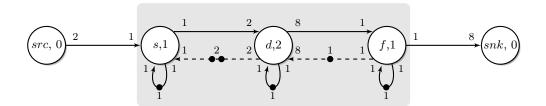

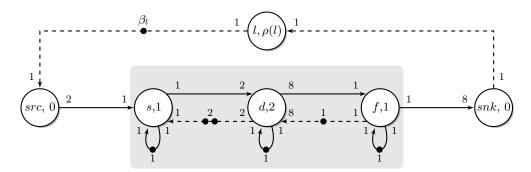

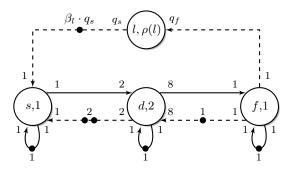

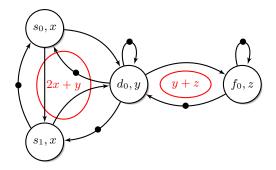

| 4.1  | An example timed SDF graph                                  |

| 4.2  | Streaming memory consistency model                          |

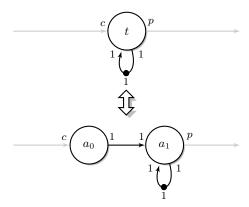

| 4.3  | SDF graph modeling a routed channel                         |

| 4.4  | Communication latency                                       |

| 4.5  | Homogeneous SDF example                                     |

| 4.6  | A state-space exploration of the example graph 50           |

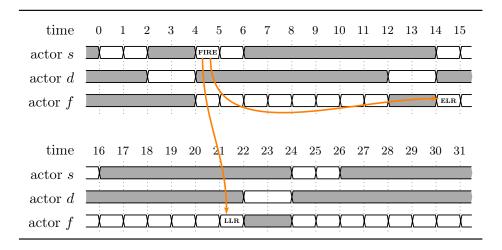

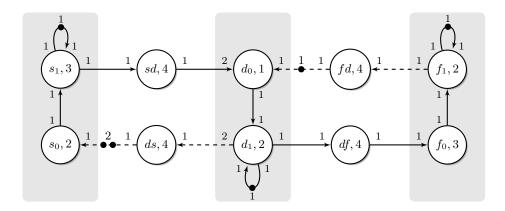

| 4.7  | Actor firings during self-timed execution of the example 52 |

| 4.8  | Example latency graph                                       |

| 4.9  | Latency constraint specified using a latency graph          |

| 4.10 | Latency constraint specified as throughput limitation       |

| 4.11 | Conversion to latency-rate servers                          |

| 4.12 | Latency-rate servers integrated                             |

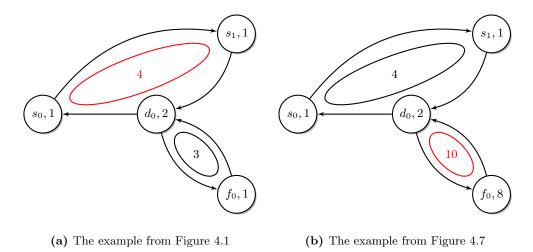

| 4.13 | Identification of critical cycles                           |

| 5.1  | Software stack                                              |

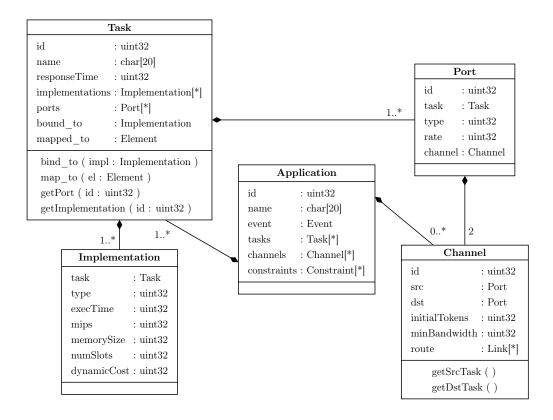

| 5.2  | Data structures modeling an application 60                  |

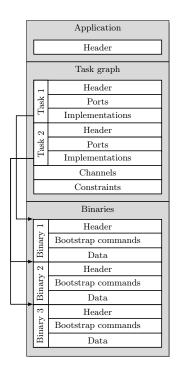

| 5.3  | The MPSoC binary format                                     |

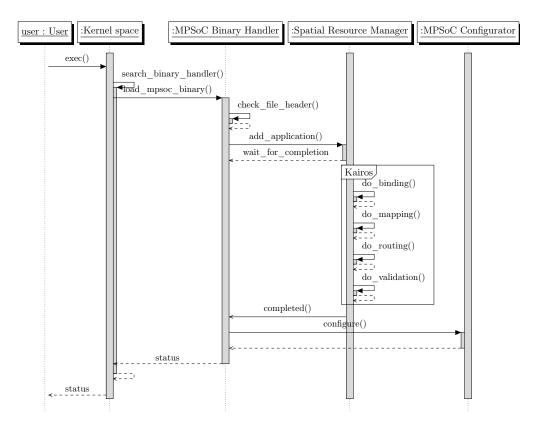

| 5.4  | Run-time workflow                                           |

| 5.5  | Faulty hardware                                             |

vi LIST OF TABLES

| 5.7 | Realview Versatile Platform Baseboard                    |

|-----|----------------------------------------------------------|

| 5.6 | External monitoring                                      |

| 6.1 | Runtimes of Kairos                                       |

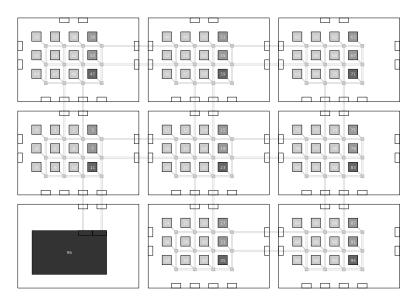

| 6.2 | Multi-tasking capabilities                               |

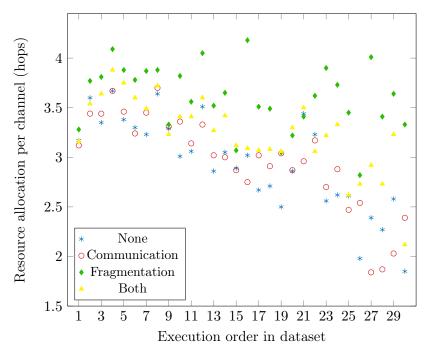

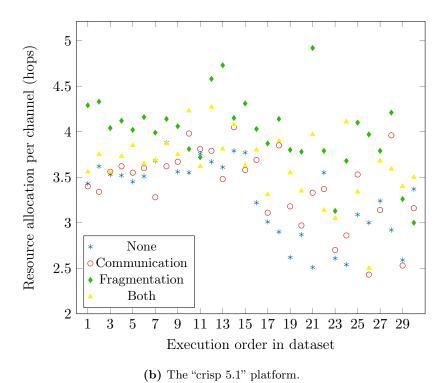

| 6.3 | Parameter evaluation                                     |

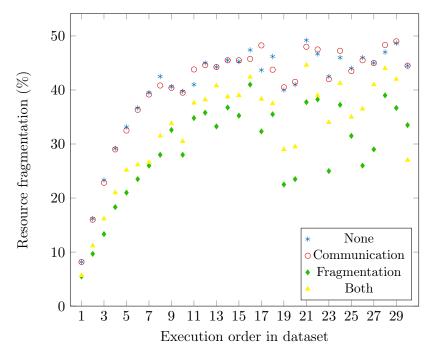

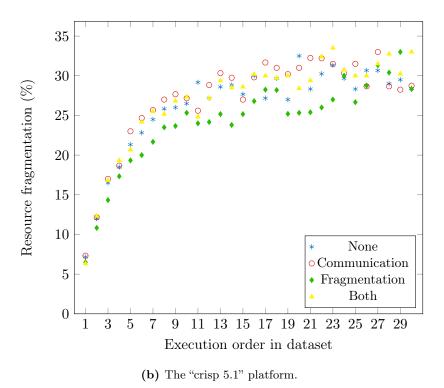

| 6.4 | External resource fragmentation                          |

| 6.5 | Average communication resources allocated per channel 76 |

| 7.1 | Parametrized HSDF graph of our example                   |

| A.1 | Basic structure of the MPSoC file format                 |

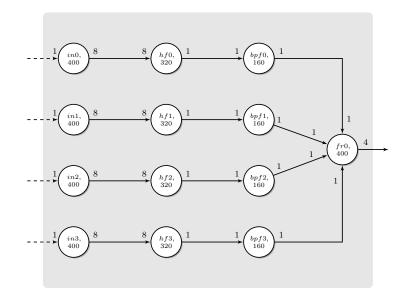

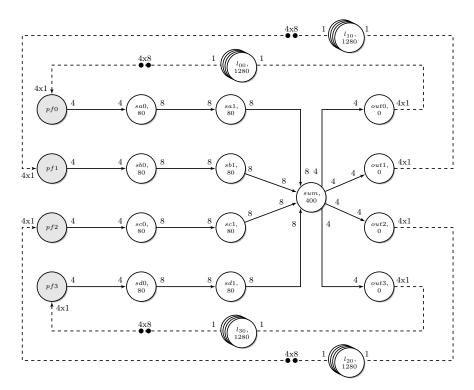

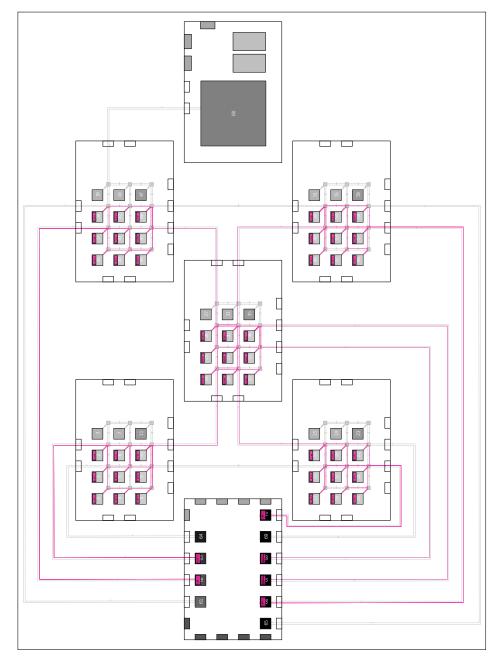

| B.1 | Specification of a beamforming application               |

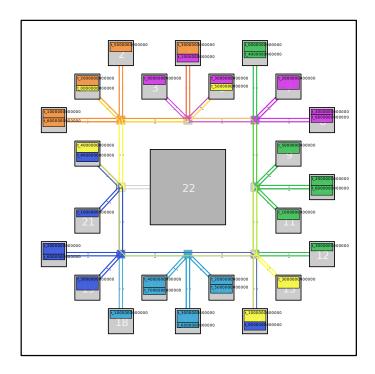

| B.2 | Execution layout of a beamforming application 90         |

# List of Tables

| 4.1 | Latency-rate properties              | 57 |

|-----|--------------------------------------|----|

|     | Quality measures available in Kairos |    |

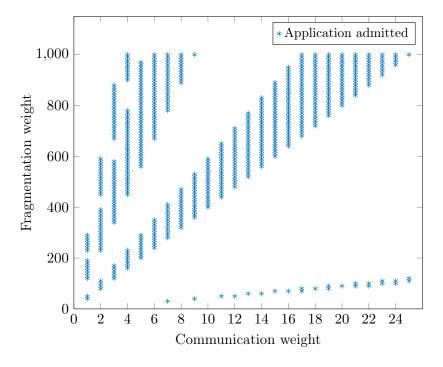

| 6.2 | Fragmentation versus communication   | 69 |

| 6.3 | Percentage of failures per phase     | 74 |

#### **CHAPTER 1**

# Introduction

One cannot buy, rent or hire more time. The supply of time is totally inelastic. No matter how high the demand, the supply will not go up. There is no price for it. Time is totally perishable and cannot be stored. Yesterday's time is gone forever, and will never come back. Time is always in short supply. There is no substitute for time. Everything requires time. All work takes place in, and uses up time. Yet most people take for granted this unique, irreplaceable and necessary resource.

Peter F. Drucker, American educator and writer, 1909

Time can be a precious resource for humans. Some tasks that need to be done take a constant time, while the duration of other tasks may depend on the amount of other resources allocated to them. Likewise, applications in computer systems require a set of resources to perform their tasks; including time.

Computer systems are subject to continuously increasing performance demands. More work needs to be done in less time, preferably with the same energy budget. Energy consumption has become a critical issue, both for high-end large-scale parallel systems [1] as well for portable devices [2]. For some application domains, like digital signal processing, specific architectures proved to deliver more performance per watt than general purpose processors. Parallel composition of domain specific processing elements and general purpose processors resulted in heterogeneous multi-core systems. Research has shown that heterogeneous systems can deliver higher performance at a given energy budget than homogeneous multi-core solutions [3, 4]. Heterogeneous Multi-Processor Systems on Chip (MPSoCs) have the potential to become the preferred architectures for high performance, low power signal processing systems [5]. This thesis thus focuses on heterogeneous MPSoCs.

Currently, the usability of such systems is still very low; it requires extensive knowledge and effort to use such a system effectively. It is difficult to write applications that integrate enough parallelism to keep all the cores of such systems busy. Also, due to race conditions, communication and synchronization issues, it is known to be more complex to write parallel applications than sequential programs [6]. Decomposition of applications into multiple tasks allows engineers

to specify and program smaller sub-problems, which can be allocated to separate processing cores. The functionality of such tasks can be implemented in various ways, depending on the target architecture, and trade-offs between performance, resource and energy budgets.

For some type of applications, especially in the domain of signal processing, it is important that some predefined performance can be guaranteed. An execution environment should be provided that allows real-time applications to meet their deadlines. To accomplish these conditions, each application should be shielded from interference with other applications in the system. The difficulty is that, for a large application domain, applications can be started or stopped by externally triggered events. At design-time, it is unknown what combinations of applications are requested to be executed during the life-time of the system, and whether enough resources can be allocated to each application. This makes it impossible to derive schedules for those applications at design-time, which is often done to ensure temporal isolation of tasks. We think of a schedule as a resource allocation plan, where each application may access resources during specified time intervals. In this sense, processor time is also considered to be a resource that is required to execute the application. In this thesis, we investigate methods to tackle this resource allocation problem at run-time.

#### 1.1 Run-time spatial resource management

A run-time resource manager has to match the resource demand of applications with the resource provision of a platform. What resources are required during its execution should be specified per application. This application specification can be used to allocate sufficient platform resources to the application. Not only the amount and type of resources required matters, but the location of those resources as well. If an application consists of multiple tasks, they may also heavily rely on communication. The communication channels between tasks thus have to guarantee enough bandwidth with acceptable latency. This spatial factor increases the complexity of the resource allocation problem, making established scheduling algorithms unsuitable for this job.

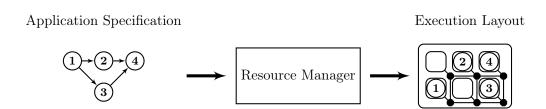

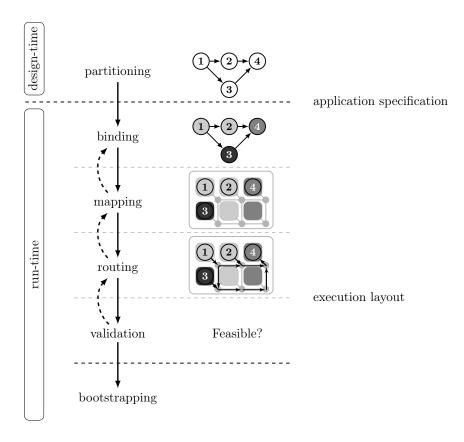

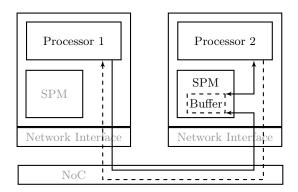

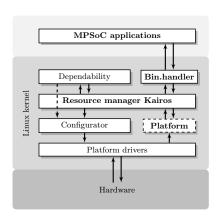

Figure 1.1: Context of run-time spatial resource management.

When successful, the resource manager provides an *execution layout* describing the amount and location of the resources allocated to that application. If no feasible

execution layout can be found, the application must be rejected. Figure 1.1 shows the context of such an environment.

The described resource management process is commonly performed at designtime using semi-automatic tools, that are often still being researched. Aside from the necessity of run-time resource management, additional benefits can be identified:

- The ability to circumvent hardware faults (fault tolerance)

- Minimization of run-time system costs (energy consumption)

- Adaption to user demands (quality of service)

- Not restricted to specific combinations of applications (use-case flexibility)

The combination of these advantages with new hardware technology cause many research projects to focus on future MPSoCs.

#### 1.1.1 The CRISP project

Within the Cutting edge Reconfigurable ICs for Stream Processing (CRISP) project [7], an MPSoC is being developed. The aim of this project is to create a scalable, reconfigurable and heterogeneous architecture that is designed to run streaming applications. Some software to support the hardware is required to deliver a working platform. The project specifically requested a resource manager, integrated in a Linux operating system, capable of running on an ARM-based processor. For demonstration purposes, it was also requested to look into methods to visualize the state of the MPSoC platform.

# 1.2 Research approach and methods

In this thesis, we investigate *spatial resource management* algorithms for run-time usage, targeting heterogeneous MPSoCs. These algorithms must run within a limited execution environment on the target platform. The main question in the evaluation of algorithms is what effort is allowed to derive an execution layout at run-time. A good understanding of the relation between the effort of the resource manager and the quality of the execution layout is desired.

Therefore, the research goal of this thesis is to create a resource manager that consists of a workflow from application specification to execution layout, as sketched in Figure 1.1. We propose a taxonomy of various phases in resource management, including a validation of the execution layout before the application is admitted to the platform; this guarantees that a minimum performance level is reached. We implement a modular prototype that allows for each phase to switch between algorithms with different approaches and various MPSoC platforms. As the number of parameters, the various algorithmic approaches, and different applications and platforms can be overwhelming, we limit this research to some reasonable alternatives.

Results are obtained using a selection of applications and three different platforms. These results are not only quantitative, as in the run-time of the resource manager, but also qualitative. For a better understanding of the resulting execution layouts, we examine possibilities to visualize the state of a platform.

#### 1.3 Structure of the thesis

A state-of-the-art survey of related resource management algorithms is described in Chapter 2. A taxonomy for these algorithms is given, which splits the resource management process into multiple phases. For each phase, we integrate ideas from related work with our own insight and requirements. In Chapter 3, a coherent set of resource management heuristics is proposed. These heuristics form the first three phases of the resource management. Traversing these phases results in a preliminary execution layout. In Chapter 4, methods are described to check whether that execution layout meets the performance constraints of the application.

We created a prototype that implements the proposed algorithms in a Linux kernel. Details of the prototype are given in Chapter 5. We present some test results using this prototype with various platforms and applications in Chapter 6. This thesis ends with some conclusions and recommendations for further research.

#### **CHAPTER 2**

# On run-time spatial resource management

In Section 1.1, we stated the research motivation to develop algorithms for allocation of resources in a running MPSoC. In this chapter, we survey the state-of-the-art in resource management at run-time. We have special interest in solutions that are tailored to heterogeneous architectures, although we investigate approaches for homogeneous architectures as well. This survey is organized in terms of relevant themes, rather than as a project-by-project summary. The discussion is presented around a taxonomy for the algorithms found in literature.

In this chapter, we separate the preparations made at design-time from the operations performed at run-time. Design-time exploration of applications is briefly discussed in Section 2.1. This process results in a set of tasks, each annotated with their resource requirements and performance characteristics. Section 2.2 states the restrictions we apply to the run-time part of the resource management process. Then in Section 2.3, a taxonomy of phases in run-time resource management is proposed. This taxonomy is used in the rest of this chapter to discuss related work.

# 2.1 Design-time preparations

An application is modeled and implemented at design-time. At this stage, characteristics of an application can be analyzed, in order to specify the resource budgets required to gain certain performance levels. We require such a specification of each application, to be used as input for the run-time resource management algorithms. Therefore, we first identify what preparations we expect to be done at design-time.

Numerous reasons exist why programming parallel architectures is difficult. The first problem is to find and to identify the parallelism in an application, known as task decomposition. Other steps involved are resource mapping, dealing with communication and synchronization issues, and avoiding race conditions. None of these steps are required to program a sequential algorithm. Some related work looks into methods to automatically extract parallelism from sequential

applications [4, 8], but manually developing applications that employ multiple processors efficiently is still more common.

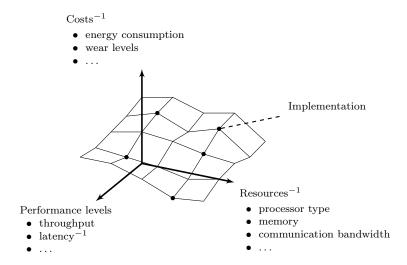

At design-time, it must be determined what resources an application minimally requires to meet its performance constraints. In general, there is a trade-off between multiple, conflicting objectives, like performance levels, resource requirements and costs. *Multi-objective optimization* may lead to a set of locally optimal solutions in the trade-off.

**Definition 1** [Multi-objective optimization] Multi-objective optimization is the process of simultaneously optimizing two or more conflicting objectives, subject to constraints.

The best solutions for multi-objective problems are called the Pareto set. For solutions from the Pareto set, it is not possible to select another solution to improve one of the objectives, without worsening at least one of the others [9]. Ykman-Couvreur et al. [10, 11] use design-time exploration to construct a Pareto set that contains multiple implementations of an application. We assume that in a similar way, design-time exploration can produce a Pareto set for each task within an application. Various implementations of a task may require a different architecture to run on, expressed in the resource requirements. Figure 2.1 shows that each implementation is characterized by an optimal combination of performance constraints, used platform resources and costs. The result of this design-time exploration can be used as input for a resource manager.

Figure 2.1: Design-time exploration of the application results in various implementations.

#### 2.1.1 Application specification

We assume that after partitioning, every application can be expressed as a dataflow model, as they are commonly used as a design abstraction for parallel

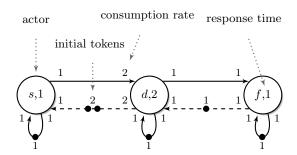

architectures [12]. More specifically, Synchronous Data Flow (SDF) graphs are widely used to specify applications, for example in [13, 14]. An entire application can be specified with an SDF graph, where the nodes in the graph represent individual tasks. The edges between the nodes model the communication channels between the tasks of the application. SDF graphs are a subclass of Petri nets. In this class, firing rules are independent of data values, so that the execution order can be determined at compile time. This ordering allows for a semi-static assignment scheduling strategy, where processor assignment can be done at the start of the application. These conditions are fit for a run-time resource manager. In Chapter 4, we reason about applications as SDF graphs, and the reader finds a more extensive introduction into SDF in Section 4.1.

#### 2.1.2 Performance guarantees and multi-tasking

A non-preemptive scheduler can be used in single-tasking execution environments. Fortunately, non-preemptive scheduling algorithms are easier to implement than preemptive algorithms, and also have less run-time overhead [15]. Once the required resources are allocated to the application, it should run without interruption, and therefore meet the performance constraints posed on the application. This assumes that the resource budgets required by the application are correctly determined at design-time.

To support multi-tasking with real-time constraints, dataflow analysis must be used to derive schedules that guarantee that hard real-time tasks will meet their deadline. As design-time analysis of all possible use-cases is infeasible when the number of applications increases, the effects of run-time scheduling have to be considered. Schedulability analysis takes worst-case waiting times into account, resulting in a very pessimistic result [14, 16]. Kumar et al. compare various analysis techniques in [14]. They show that all the proposed techniques in the multi-processor domain that provide guarantees, have a low utilization. Kumar et al. [14] worked on a technique that improves utilization, by sacrificing the ability to provide hard real-time performance guarantees. Therefore, most known solutions that support multi-tasking do not provide hard real-time guarantees.

Wiggers et al. [17] show that the accuracy of the analysis can be improved by modeling run-time scheduling with latency-rate servers. The amount of improvement over a model with response times is not be given for the general case. Suitable scheduling algorithms for dataflow analysis are Time-Division Multiplex (TDM) and round-robin, which are both latency-rate schedulers [16].

Although we state that a multi-tasking environment adds an undesired complexity in the context of this research, we must allow applications to share resources where possible, because otherwise the flexibility and efficiency of the system would be too low. One can think of shared memory, communication lanes and other system support functions. The resource manager must arbitrate over these resources, and grant applications access to them to fulfill their resource requirements.

#### 2.2 Assumptions for spatial resource management

The resource manager usually runs on one of the Processing Element (PE) of the MPSoC, having authority over the other resources in the system. Work presented in [18] states that centralized Run-time Spatial Resource Management (RSRM) has disadvantages in the context of hundreds or even thousands of cores that may be integrated in a System on Chip (SoC)<sup>1</sup>. Arguments are scalability issues, a single point of failure and communication hot-spots.

In [18], Faruque et al. propose a distributed solution that uses a two-step approach. An application is first forwarded to a cluster with enough available resources, and then the cluster agent has to deal with a problem similar to the general, centralized approach. While a distributed solution for resource management may be required for future designs, we first have to find a good approach to solve the problem for small systems (i.e. a cluster).

When a new application arrives, the RSRM must select suitable implementations from each Pareto set of the application's tasks. Picking the most suitable implementation depends on the current state of the MPSoC, and the optimization objectives the end-user has in mind. The resource manager determines if the resource requirements of the application can be fulfilled.

With arbitrary intervals, applications are incrementally added to the MPSoC, as done in [13, 19]. The resource manager must isolate the tasks that are already present on the system, from the unmanaged application. A resource management policy, mentioned in [14, 20], should enforce such conditions:

- admission control an application is only allowed to start if the system can allocate, upon request, the resource budget it requires to meet its performance constraints.

- guaranteed resource provisions the access of a running task to its allocated resources cannot be denied by any other task.

If an application can not be added to the system without violation of this policy, the application must be rejected. To resolve a failure, either the application or the platform state have to be changed. Changing the resource requirements of the application will be discussed in Section 2.3.1. Altering the platform state can be done by migration of running tasks.

#### 2.2.1 Task migration

In the long run, it may be beneficial for the resource manager to be able to migrate tasks from one PE to another. Such a migration may result in less operational costs, allow Quality of Service (QoS) changes and load-balancing, or increase the success rate of future resource allocation attempts. Another reason may be that a PE must be cleared for dependability test-access [21].

1. Note that of today (2009), few heterogeneous SoCs are production ready, and those that are, contain no more that 10 processing elements.

New processor technology tends towards incorporating hardware support for live migration between processors [22]. To the best of our knowledge, this is only done in high performance processors, aiming at usage in virtualization servers. A hypervisor, also called Virtual Machine Monitor (VMM), initiates and controls the migration process. Even with hardware support, first a virtual machine is suspended; its state is captured and moved to another virtual machine, where it is resumed. In high performance systems, the latency involved is accepted, such that this migration process is considered to be "seamless". Also, the hypervisor plays an essential role to handle difference between types of processors properly. Currently, it is only possible to migrate virtual machines within a subset of x86-based processors. The CPUID instruction is used to query the processor's capabilities, which is processed by the hypervisor to avoid incompatibility issues [23].

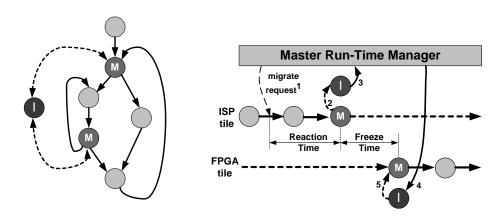

In the way we consider MPSoC platforms, no hypervisor is running on the individual PEs. A migration solution then requires external intervention. For hard real-time applications, migration points should be defined so that the guarantees are not violated. A migration point in a task is a state in which all relevant information can be captured and transferred to another PE. Figure 2.2 shows a task migration process. After a migration request is issued, a reaction time is experienced until a migration point "M" is reached. At a migration point, the state "T" can be extracted and transported to another element. The performance of the task suffers from a freeze time, until the task resumes its execution.

Figure 2.2: A migratable task containing two migration points M and an interrupted state I. At a migration point, the state is transferred to another PE, where the task continues [24].

Considering streaming applications, it is difficult, or even impossible, to integrate this approach in combination with performance guarantees. To reduce the delay between a migration request and a migration point, a task should have many migration points. The resulting overhead of checking for pending migration requests at every migration point is the main issue in task migration [24]. All software-based approaches have a significant performance overhead during normal execution. Nollet et al. [24] propose a hardware supported task migration technique

for heterogeneous MPSoCs. This solution is hardware specific and lacks support in compilers and other tools.

In [25], experiments with the migration of various applications on an ARM architecture were analyzed. In the baseline case, the average downtime during migration was 22 seconds, ranging from almost 0 seconds to 95 seconds. The larger part of the downtime was devoted to serialization and deserialization of the task state. Zhang and Pande [25] developed a static compiler analysis method to decrease the migration overhead by pre-serializing the state in a program. For their test cases a little performance degradation of 2% was experienced. With this improvement, the system state still needs to be transmitted and deserialized, which still took, on average, 8.5 seconds, with 36 seconds being the worst case. Indicated by related work, task migration must be considered infeasible, and is therefore not considered in this research.

In the next section, we define multiple phases in resource management. We assume that once these phases are successfully traversed, an application will be executing on the target platform until the application is completed. As task migration is not possible, any decision made during the resource allocation process is fixed for the lifetime of the application.

### 2.3 Taxonomy for spatial resource management

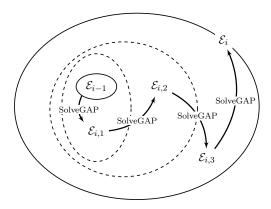

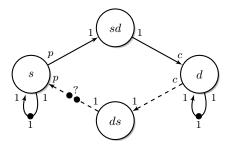

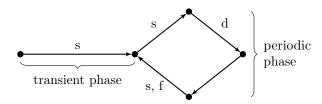

Finding an optimal solution to add applications to an MPSoC is very complex. To avoid this complexity, most researchers split the problem into multiple subproblems. In this section, we present a taxonomy for these sub-problems. For brevity reasons, a specific ordering is assumed, but different orderings exist as well. Each sub-problem is attacked iteratively in a separate phase, with reduced complexity compared to the original problem. Hölzenspies et al. [13] names such a work-flow hierarchical search with iterative refinement. The heuristics we found in literature can be classified into four phases:

- 1. Binding: for each task of the application, an implementation is selected that is able to execute the task with low cost or high performance. The resource requirements of the chosen implementations, including the type of architecture for execution, must be satisfied to admit the application.

- 2. Mapping: taking locality into account, specific resources are assigned to each task, such that the resource requirements of the implementation chosen in phase 1, are fulfilled.

- 3. Routing: for pairs of tasks that need to communicate, communication links are established between the processing elements assigned to them in phase 2. The amount of communication resources required is taken into account.

- 4. Validation: the performance constraints that are specified in the application specification are validated against the performance that is guaranteed by the execution layout derived in the previous phases.

Figure 2.3 illustrates this taxonomy. With the "partitioning" phase, we indicate the software development effort at design-time, as described in the beginning of this chapter. We only consider the binding, mapping, routing and validation phase to be part of a run-time resource manager. As a result of these phases, an execution layout is provided. Based on those instructions, platform specific software can configure the hardware accordingly and start the application, which we indicate with the "bootstrapping" phase.

**Figure 2.3:** Various phases of a resource management algorithm. Note that application partitioning is typically done at design-time, while the other phases are performed at run-time.

In works that consider homogeneous architectures, the binding phase is irrelevant. That is also the case for applications that only have a single implementation for each task in the application, which may be considered as binding at designtime. All related work considers the mapping phase. In some approaches, the routing phase is not considered as part of the resource management problem or it is considered trivial, whereas in other works [19, 26, 27], the mapping phase is subordinated to the routing principle. The following sections categorize and describe the various approaches found in related work, according to this taxonomy.

#### 2.3.1 Binding

The binding phase is the first step in the resource manager. Every task of the unbound application should be executable by at least one type of PE. From the set of unoccupied PEs, the resource manager should pick a PE type that is supported by the task. When PEs of multiple types fit, the Run-time Spatial Resource Manager (RSRM) makes a choice based on the task's desirability for some PE type. The most important part of heuristics in this phase of resource management are the criteria that express this desirability. This choice also defines the order in which tasks are bound, which is important for the final result, especially when the target system has few available PEs left.

To make the best binding choice possible, the entire set of tasks to be bound could be considered at once. This problem can mathematically be modeled as a Multi-dimensional Multiple-choice Knapsack Problem (MMKP). In [11], an MMKP formulation is used to obtain exact or near-optimal solutions for allocation of resources. However, an MMKP is NP-hard, making it not very suitable for runtime usage. Considering every possibility in the search space, Ykman-Couvreur et al. [11] developed a fast heuristic for solving the MMKP. Their heuristic reduces the multi-dimension resource requirements of each item into a single resource combination with a certain cost. Sorting them by value per resource combination can be considered as a notion of desirability. The last step is a greedy algorithm that optimizes the total value of the chosen resource combinations until there is no better feasible solution available. This greedy selection can be applied to any sorted optimization points. While this approach is derived from a mathematical formulation of the optimal solution, simpler sorting algorithms may lead to similar results. Other works use energy consumption [13, 18] or execution time [28] as an ordering criteria. Faruque et al. [18] specify the energy consumption of a PE type with two values, namely static and dynamic energy. Hölzenspies et al. [29] differentiate in energy consumption per architectural type, normalized by their processing capacity.

Generally, after ordering the unbound tasks by their desirability, the tasks are bound to the preferred architecture. We found no related work that explicitly mentions the case where the system runs out of resources during the binding phase. Kim et al. [30] evaluate heuristics for scheduling in a heterogeneous environment. They consider an oversubscribed system, such that not all tasks can be performed by the system. But the tasks considered in [30] are independent, so that no communication or dependency exists between tasks. A task that cannot be executed, does no harm to the other tasks in the system. Considering an application that consists of multiple dependent tasks, it is probably not useful to bind less than the whole application.

#### Binding at design-time

In [31], two types of tasks are considered: hardware tasks and software tasks. In this approach, the binding of tasks to a specific architecture is inherited from the

application specification. Hardware tasks must be executed in reconfigurable logic or dedicated IPs, while software tasks can run on any processor. While there is an architectural difference in PE on a hardware level, the mapping algorithm of [31] only differentiates between hardware and software tasks.

#### Combining the binding and mapping phase

Nollet et al. [28] calculate the normalized task execution time variance  $(V_{Ni})$  for each supported PE. Tasks with a high  $V_{Ni}$  value are very sensitive to which PE they are assigned to, and those tasks should preferably be bound before other tasks. The downside of this approach is that the execution time is decoupled from the other characteristics of task implementations. For example, in terms of energy consumption it may be beneficial to bind a task to a PE that takes more execution time, as long as it does not violate the task's constraints. The binding priority of the unbound task is defined by  $V_{Ni} \times C_i$ , where  $C_i$  is a communication requirements factor. Nollet et al. [28] sort the tasks to their priority, and order the PEs on their load and available communication resources. In a single iteration, the tasks are iteratively mapped to the best fitting PEs. In their case, reconfigurable hardware often has the highest preference. Therefore, an adhoc heuristic re-evaluates the choice, to avoid wasting this scarcely available PE type. We think it is difficult to apply this algorithm in a system with more architectural types.

#### 2.3.2 Mapping

Many works that consider the mapping problem assume a homogeneous architecture. This clearly provides a high flexibility in assignment of tasks to PEs. Because heterogeneous systems pose more restrictions on the mapping procedure, it is presumably harder to obtain a good mapping. In general, the same optimization criteria may apply for both cases. Given the binding decision from the previous phase, optimization towards locality is generally used during the mapping phase. The intention is to minimize communication costs and to prevent a high fragmentation of the available resources after the mapping phase. In this section we describe various approaches in mapping applications onto an MPSoC.

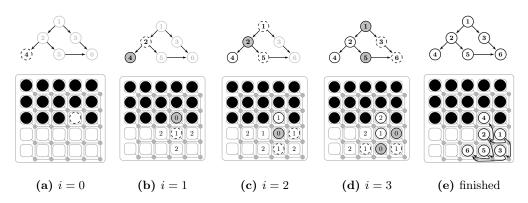

#### Fragmentation

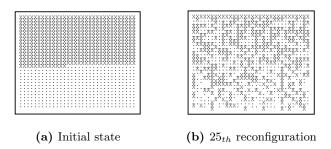

As tasks can not be migrated, a mapping is fixed for the lifetime of an application. This requires a mapping algorithm to consider fragmentation of the platform's resources. In Figure 2.4, two applications are mapped to a platform, using a simple linear allocation method. The first application is denoted with "x" and the second with ".". In each step, the resources required by one of the applications are allocated or de-allocated, while their precise resource requirements are varied over time. As can be seen in the figure, the platform is highly fragmentation after 25 time steps. The sum of the resources required by the application may be smaller than the available resources in the platform, but the routing may fail if

the resources are too widely spread over the platform. Resource fragmentation must thus be taken into account, as future resource allocation attempts are more likely to fail when the fragmentation increases.

Figure 2.4: Resource fragmentation of a platform with two applications [32].

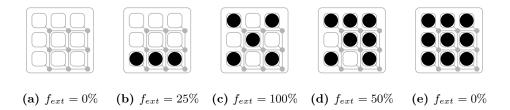

Platforms suffer both from internal and external fragmentation of available resources. A task may not employ an element to its fullest, leaving some percentage of the available resources unused. *Internal fragmentation* is the result of allocating a set of resources that does not precisely fit a certain amount of elements. *External fragmentation* results from allocation of non-adjacent PEs, as in Figure 2.4. In [33], these terms are expressed as ratios to the total amount of resources. In related work, fragmentation is not always considered, or sometimes only dealt with implicitly. For example in [20], algorithms are "adjusted to fill up partially filled PEs" to reduce internal resource fragmentation. The trade-off between fragmentation reduction and other objectives like minimal energy consumption or communication usage is not mentioned.

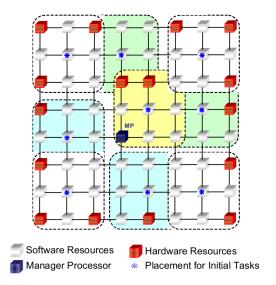

#### Cluster-based mapping

An implicit cluster-based approach is proposed by [31]. Each application has a "master" task that issues requests for the mapping of "slave" tasks. To initialize the system, only the master tasks are mapped. Carvalho et al. [31] illustrate that random mapping of these tasks may result in undesirable scenarios. For more careful mapping, a method is adopted that defines clusters of PEs for each application, and the initial master tasks are placed inside a cluster. In the example of Figure 2.5, the platform has been divided into nine clusters and each cluster is composed of nine PEs. Because these virtual clusters overlap, an application can use resources from another cluster. Unfortunately, this approach can not support more applications than the number of defined clusters, as this would require some sort of re-clustering strategy. Carvalho et al. [31] argue that this constraint is required to prevent application deadlock when the system runs out of resources.

Master tasks communicate with the *manager processor* (MP) to request and release resources. When a slave PE is requested, the mapping algorithm has to select a PE from within the application's cluster. This simplifies the mapping procedure, where mapping decisions in the overlapping zones of clusters are most interesting. This view of application mapping is very different from the general

Figure 2.5: Cluster-based mapping. Dashed lines denote the cluster limits [31].

perspective. In general, the applications are mapped incrementally, but in this approach the tasks that compose the application are mapped incrementally, upon request of the master task.

The overall performance highly depends on the initial placement. The research of Carvalho et al. [31] lacks details of the method used for creation of clusters, and how to adapt to arrival and departure of applications. Also, some responsibility for bootstrapping the application is moved from the resource manager to the application's master task. This results in less distribution transparency and increased communication overhead, which are both not desirable.

Faruque et al. [18] also use a cluster-based approach to narrow the search space when the MPSoC is large. First, a cluster negotiation algorithm is started to find a cluster for the application. If no suitable cluster can be found, task migration requests are issued to free resources in a particular cluster. If no suitable cluster can be delivered, a re-clustering algorithm negotiates between the requesting cluster and its neighbors to exchange some PEs. This may or may not result in enough available resources to map the application. For resource management inside a cluster, Faruque et al. [18] use the algorithm of Hansson et al. [34]. That algorithm was originally developed for usage at design-time. A cost function is used to decide to which PE of a particular architectural type a task should be mapped. For a task  $t_i$ , the selection of PE  $n_i$  yields a certain cost  $c(t_i, n_i)$ :

$$c(t_i, n_j) = \alpha(D(n_j) + bw_t(n_j) + RR(n_j))$$

$$+\beta \sum_{k \in T_{con,m}} d(k)vol(k)$$

where  $D(n_j)$  is the average distance of  $n_j$  to all other PEs of the cluster,  $bw_t(n_j)$  is the total bandwidth requirement of the tasks on  $n_j$ , and  $RR(n_j)$  is the resource

requirement of  $n_j$ . The last factor is the sum over the set of all connected and mapped tasks  $T_{con,m}$  of the Manhattan distance d(k) between the mapped tasks, times their communication volume vol(d) [18]. The unmapped tasks are sorted first by availability of PE types, and secondly by their bandwidth requirements. By evaluation of the cost function  $c(t_i, n_j)$ , a PE is selected iteratively for every task. The weights  $\alpha$  and  $\beta$  in  $c(t_i, n_j)$  are not given in [18], but they give some flexibility for optimization of the cost function for a specific system. Faruque et al. [18] claim to have a less complex mapping algorithm than the first algorithm described in this section (Carvalho et al. [31]), but they do not give results in terms of any other performance measure.

#### First Fit mapping

In some works [13, 20], the low-complexity First Fit (FF) algorithm is used for the initial mapping of tasks to PEs. After this greedy assignment, Hölzenspies et al. [13] try to improve the quality of the mapping by relocating tasks. Iteratively for each task, an attempt is made to find a better assignment by probing other locally available PEs of the same type. In this operation, it is allowed to swap two tasks that are mapped to the same PE type. When the assignment does not improve, the previous mapping is restored.

Moreira et al. [20] support multi-tasking by mapping tasks to intermediate Virtual Tiles (VTs). Then, each VT is assigned to a physical PE, taking communication channels into account. The First Fit with Clustering (FFC) algorithm of Moreira et al. [20] is more tailored to their architecture than a general FF algorithm. In their architecture, each router is connected to three PEs, making it desirable to map heavily communicating tasks to the same cluster (of three PEs). Although the FFC algorithm decreases bandwidth usage, it has an adverse effect on the mapping success rate when the system becomes saturated [20]. Therefore, Moreira et al. [20] use an unclustered version of their algorithm when FFC fails. We think that a more general mapping algorithm can also perform well on this architecture, if the internal communication links in the cluster are considered less costly than a single hop, increasing the preference to use local elements first. Doing so, the desirability remains to map heavily communicating tasks close to each other.

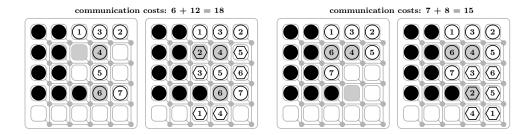

#### Mapping with region selection

Figure 2.6 shows two alternative mappings of two applications, where after mapping the second application, fragmentation of the available PEs becomes significant (see: Figure 2.6b). Chou and Marculescu [19] use a region selection procedure to allow for a more effective mapping for any subsequent applications (see: Figure 2.6c). The region is obtained by picking PEs around the initially chosen PE that have the lowest total value by the following definitions:

**Definition 2** [Dispersion factor] The dispersion factor D(e) of a PE e, is defined as the number of idling neighbors of that PE.

**Definition 3** [Centrifugal factor (C)] The centrifugal factor C(e) of a PE e, is defined as the Manhattan distance between PE e and any PE at the border of the region occupied by the current application.

A PE that has most of its neighbors utilized, *i.e.* it has a small dispersion value, is very likely to be later isolated; selecting this PE to be utilized for the application mapping helps reducing the external fragmentation. A PE with the smaller centrifugal value is better suited for selection, since it increases locality of the tasks in the current application.

(a) Two applications that have to be mapped

- (b) Greedy mapping approach.

- (c) Mapping approach with region selection.

**Figure 2.6:** An example of two approaches in incremental application mapping on a heterogeneous MPSoC, where both the degree of fragmentation and communication costs play a role.

After a region has been determined by selecting the right amount of PEs according to these definitions, the resource manager attempts to find the best mapping within that region. Any of the procedures described earlier can be used to allocate PEs within the selection region to some optimal goal. Chou and Marculescu [19] propose the *node coloring* method, described in the next section, which aims at low inter-processor communication. The region selection algorithm shows a 25% reduction in inter-processor communication compared to the same mapping algorithm without the region selection strategy. The proposal of Chou and Marculescu [19] best suits dense application graphs, while a sparse graph could have a straight line of PEs as a very good solution. Thus, for optimizing inter-processor communication, it is sufficient (and more general) to minimize the distance between neighboring nodes, like in [13]. Unfortunately, the authors

do not evaluate the mapping success rate, which we expect to increase when the degree of fragmentation is lowered.

#### Node coloring

Chou and Marculescu [19] use a node coloring technique to map an application on the PEs of the selected region. Note that colors used are unrelated to Figure 2.6, but indicate the progress of the algorithm. Every task that needs to be mapped is initially white. When a suitable PE is found, it is grayed, and is made black when the allocation is fixed. Tasks that have to be mapped are sorted per PE type, and ordered by decreasing communication demands. Starting with the first task of the smallest PE set, select available PEs of the correct type to map this task. Then the task is colored gray. If any neighbor (in the application graph) is either gray or black, the task is assigned to a specific PE, such that the distance to its neighbors is minimized. Afterwards this task is colored black.

#### 2.3.3 Routing

After each task has been mapped to an element in the platform, we have to make sure that the positions of those elements allow tasks to communicate with each other. Communication links between tasks may be subject to latency constraints and bandwidth requirements. The communication data must be routed through the network in such a way that these requirements are met. If larger communication volumes are spatially clustered, non-optimal routes may have to be used to provide the required amount of communication resources. If tasks have a non-constant communication volume during their lifetime, routing decisions have to be made in both the spatial and the temporal domain.

When the capacity of a physical link between two routers is depleted, an alternative, probably longer route may work around this network congestion. This is a suitable solution to fulfill the bandwidth requirements. However, latency constraints are very sensitive to longer routes, and therefore should be given a higher priority over bandwidth constraints. Srinivasan and Chatha [27] have a priority based policy in their solution for design-time routing on Network on Chip (NoC) architectures. Their approach ensures that links with tight latencies are given priority over links with high bandwidth requirements (and more relaxed latencies). Every communication link c that must be routed is ordered to descending priorities:

$$\rho(c) = \frac{bandwidth(c)}{latency(c)^k}$$

An integer k is determined, such that the communication link with the highest bandwidth requirement,  $c_i$ , has a lower priority than the link with the tightest latency constraint,  $c_j$ :

$$\frac{bandwidth(c_i)}{latency(c_i)^k} \le \frac{bandwidth(c_j)}{latency(c_j)^k}$$

(2.1)

Alternatively, Chou and Marculescu [19] define an architecture that has a separate data and control network. These networks are separated to ensure that data transmission does not interfere with the control messages generated by the Operating System (OS), which are considered to be more sensitive to latency. In their algorithm, the routing phase is not considered, because in the mapping phase it is assumed that PEs are only selected when the bandwidth requirements are met. Chou and Marculescu [19] do not explain how this check is performed.

In [31], the occupation of the NoC is measured using five mapping heuristics. To compare the approaches, the NoC topology, the routing algorithm and the communication delays are modeled. The best performing mapping heuristic is "Path Load", which minimizes the occupation of the internal links of the NoC for each new task inserted in the system.

Moreira et al. [20] use a network graph model that incorporates time slots. A router consists of T nodes, where each node represents a time slot. Physically connected routers are modeled by connecting the time slots of the routers in the graph, shifting 1 slot to represent the 1-slot delay between routers. This approach reduces path finding and slot allocation to a single problem, at the cost of a larger and denser network graph. The problem of finding several paths in this network graph is known as the *Directed Edge-Disjoint Paths Problem*. Because this problem is NP-complete, Moreira et al. [20] use the *Shortest Path* approach instead, finding one route at a time instead of all paths at once. What percentage of the bandwidth can be reserved depends on the control overhead introduced by the resource manager.

#### NoC architectures

A NoC has a limited number of *physical channels* between each router. For example in [35], two routers are connected by two unidirectional links in opposite direction. There is often a demand for more than one communication channel between two routers. Like we discussed in the previous paragraph, time-sharing can be used to split communication resources between multiple applications. Doing resource management at run-time requires accounting of all time slots distributed over the interconnect at a central point.

In [35], a physical channel is time-shared using *virtual channels*. The resource manager allocates for each communication channel a virtual channel through each router in the communication route. The router arbitrates over a physical channel, splitting the available bandwidth between the allocated virtual channels. This arbitration can be implemented for example with round-robin, optionally with different budgets per virtual channel.

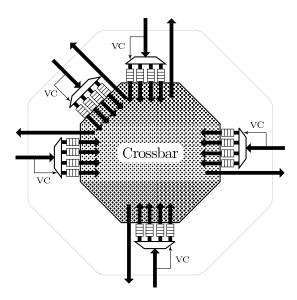

Due to hardware restrictions, there are a limited number of virtual channels per physical channel, the number of connections is also still limited. Kavaldjiev et al. [35] propose the "GuarVC" NoC router, and they state that 4 virtual channels per physical link is a good choice when considering router area and communication throughput [36] (see Figure 2.7 for a schematic of the "GuarVC" architecture). Each virtual channel can be configured to provide guaranteed throughput (GT)

or best effort (BE) services. A GT channel should provide services to a single connection only, so that a certain bandwidth with a maximum latency can be guaranteed. Less demanding traffic can use a BE channel, that can be shared adhoc among multiple connections.

Figure 2.7: The "GuarVC" NoC router.

#### 2.3.4 Validation

Even if enough communication resources were allocated to the application, the question remains whether the application performs well enough. We use the validation phase to validate the performance of the execution layout against the performance requirements of the application. This phase may be skipped by applications that do not have any performance constraints.

In [14, 20], an application is specified as an SDF graph. Kumar et al. [14] evaluate the performance of an application mapped to a MPSoC platform. A combined model of the platform and the application can generate performance figures, such as throughput and processor utilization. These results are obtained at design-time, and are used to create a resource manager. The resource manager then monitors the applications at run-time, and intervenes to ensure that all the applications are able to meet their throughput requirements. It is however not guaranteed that every constraint is honored at all times.

All related work on validation methods are still used at design-time. In Chapter 4 we discuss some related work that we use to realize the validation phase at run-time. That approach uses SDF graphs as well.

#### 2.4 Optimization criteria

For comparison of the proposed algorithms in various works, a performance measure has to be defined. In some works [11, 18], computational effort is regarded as a performance measure. However, we consider algorithm complexity a design constraint like in [27], rather than an optimization criteria. An acceptable delay for the application to start executing on the system is at least 10ms, as this is the order of magnitude to start a new application in a Linux OS [11, 19]. This is due to the interrupt timer being set to 100 Hz. Depending on the target platform, this tight constraint may be relaxed. An upper bound on the algorithm complexity is that a solution must be computed faster than the anticipated average arrival rate of new applications [30]. As this period is relatively long in embedded systems, it is also not a realistic estimation of the acceptable delay that may be introduced by the resource manager. We claim that no universal constraint can be formulated in terms of computational complexity.

If it is possible to fulfill the request to execute a certain application, the system has to allocate the resources to that application, no matter what costs are involved. At the point where the system becomes saturated, both the availability of resources and the fragmentation degree of resources determines whether an application is still mappable. Benchmarking the algorithm with numerous scenarios, as done in [20, 27, 28], gives an estimation of the mapping success rate. We think that this rate is the most important factor for measuring the quality of the solution. Given a constant success rate, we can optimize the solution towards other performance measures, such as energy consumption.

We mentioned in this chapter that energy consumption is the main advantage of heterogeneous platforms. However, estimating energy consumption is very complex, due to the many relevant factors [37]. This is illustrated by the fact that all works that consider energy consumption use different energy consumption models. For example, Wolkotte et al. present in [38] some energy models that compare two NoC architectures with a shared-bus architecture. The derivation of those models shows that the final equation is highly dependent on the architecture and the technology of implementation. But once such an equation is derived, it is rather simple to use. However, if we do not want to know absolute energy consumption values, we can simplify the energy model in [38] by stating that less hops in the NoC cost less energy, which is trivial. Unfortunately, for the most important decision that takes energy consumption into account, the binding decision, it is unclear what energy model could be used as an optimization criterion.

Altogether, it is hard to compare the various approaches described in this chapter in qualitative terms. We think that there is a need for a generally applicable algorithm, that can be fine-tuned by specific objective functions. In the next chapter we describe heuristics for each resource management phase. At various points, these heuristics can be instructed to optimize towards some objective, such as high performance or low energy consumption.

#### **CHAPTER 3**

# Heuristics for spatial resource management

The previous chapter discussed related work on spatial resource management. Following the decomposition of spatial resource management into phases, we propose a coherent set of heuristics for the implementation of a resource manager. Where relevant, we refer to the previous chapter to show similarities between this work and related work.

In the first part of this chapter we introduce some notation and assumptions about platforms and applications. We model both a platform and an application as a directed graph, but we need a distinct notation for both graph types to show relationships between them. Using this notation, we give specific algorithms that implement the binding, mapping and routing phase of spatial resource management.

# 3.1 Hardware platforms

In this section we describe the MPSoC platforms that can be managed by the resource manager. We do not want to limit our research to a specific platform. Therefore, we introduce an abstraction of a platform and its resources as a graph. We think of a platform as a number of elements, each capable of performing some task. Each element has a communication interface to the interconnect of the platform. Within the interconnect, routers are able to direct traffic along communication paths. Various types of communication architectures are possible, but an interconnect always has to provide predictable services. We define the interconnect of a platform as a directed graph  $\mathcal{N} = \langle \mathcal{R}, \mathcal{L} \rangle$ , where  $\mathcal{R}$  is a set of routers, and  $\mathcal{L} \subseteq \mathcal{R} \times \mathcal{R}$  represents the communication links between routers. The set of elements  $\mathcal{E}$  interfaces with the interconnect through their communication interfaces  $\mathcal{F} \subseteq \mathcal{E} \times \mathcal{R}$ . Combining all the components, we obtain a platform graph  $\mathcal{P} = \langle \mathcal{E} \cup \mathcal{R}, \mathcal{L} \cup \mathcal{F} \rangle$ .

Each component in such a platform provides a limited amount of resources. Like in [29], we express those resources as *capacity vectors*. For each component, a capacity vector C(x) indicates the remaining resource provisions of component x. All capacity vectors for the same kind of components (elements, routers, lanes

and interfaces) have the same dimension. These dimensions are orthogonal, i.e. the members of a capacity vector are independent. Thus, in our definition of a platform, we have the capacity vectors  $C_{\mathcal{E}}(e)$ ,  $C_{\mathcal{R}}(r)$ ,  $C_{\mathcal{L}}(l)$  and  $C_{\mathcal{F}}(f)$ , denoting the capacities of an element e, router r, communication link l and communication interface f respectively.

Architecturally different hardware components are used to compose heterogeneous platforms, or to build multiple different platforms. Each type of hardware component may have different capabilities. A *microarchitecture* is the realization of an Instruction Set Architecture (ISA) onto a processor. Processors with the same ISA are capable of executing the same tasks, not considering external restrictions such as limited memory capacities. The performance of a task might vary among microarchitectures with the same ISA.

**Definition 4** [Architecture] Let  $\chi$  be a finite set of different microarchitectures. We define the subset of elements  $\mathcal{E}_{\tau} \subseteq \mathcal{E}$  to be of architectural type  $\tau \in \chi$ . Likewise, heterogeneous interconnects can be modeled with architecturally different routers  $\mathcal{R}_{\tau}$ .

Within the set  $\mathcal{E}_{\tau}$ ,  $\mathcal{R}_{\tau}$ ,  $\mathcal{F}_{\tau}$  or  $\mathcal{L}_{\tau}$ , a component may have distinct amounts of remaining resource capacities, caused by design choices, asymmetric resource allocation or hardware failures. Whether a platform can support an additional application thus depends on the available architectures, remaining resource capacities, and their location. First we introduce the definition of an application, after which we continue to discuss the spatial resource management problem.

# 3.2 Applications

Each application defines a set of resource and performance constraints. Tasks pose resource constraints on the elements they are assigned to, while channels demand a certain bandwidth for communication between tasks. Altogether, they have to reach a minimum performance level.

We define an application to be either a single task, or multiple tasks connected with communication channels. An application can be formally described as a set  $\mathcal{T}$  of tasks and a set  $\mathcal{C}$  of communication channels:  $\mathcal{C} \subseteq \mathcal{T} \times \mathcal{T}$ . The application  $\mathcal{A} = \langle \mathcal{T}, \mathcal{C} \rangle$  is a weakly connected directed graph, which means that no disjoint sub-graphs can exist in the application graph.

**Definition 5** [Connectivity of a directed graph] A directed graph is weakly connected if there is an undirected path between each pair of vertexes, and strongly connected if there is a directed path between every pair of vertices [39].

For each task  $t \in \mathcal{T}$ , a nonempty set of *implementations*  $\mathcal{I}(t)$  must be provided. The implementation of a task is an interpretation of its functionality, mapped to a specific architecture. Implementing the functionality of a task often entails a tradeoff between performance, energy consumption and development effort. A software developer can thus create multiple, reasonable implementations for a single

task, shifting the tradeoff decisions from design-time to run-time. Other grounds to allow multiple implementations per task are ways to provide multiple QoS levels, and improved utilization by working around shortage of specific resources.

Analogue to the definition of elements, a set of implementations can be partitioned based on the architecture it requires for execution:  $\mathcal{I}_{\tau}(t)$ . Thus, the subset  $\mathcal{I}_{\tau}(t) \subseteq \mathcal{I}(t)$  contains implementations that can be mapped to elements of architecture  $\tau$ . An implementation i is then characterized by a requirement vector  $R_{\mathcal{I}}(i)$ , also known as demand vector [29, 40]. Such a requirement vector contains the minimal set of resources required to perform the task correctly. Opposed to the capacity vectors given in the previous section, we also have a requirement vector  $R_{\mathcal{C}}(c)$  for each channel  $c \in \mathcal{C}$ .

Any arbitration over shared resources must ensure that every partioning of resources denoted by the capacity and requirement vectors ensures *composability*. A platform is defined to be composable if the functional and temporal behaviour of an application is not influenced by the presence or absence of other applications on the platform [41]. A composable platform allows us to redefine the resource allocation problem in terms of a single application and a set of remaining resources. This is an important assumption when we deal with the spatial resource management problem.

### 3.3 The spatial resource management problem

The resource management problem we address in this thesis is somewhat similar to the Multilevel Generalized Assignment Problem (MGAP), which was first described in [42]. The MGAP was formulated for a scenario where machines in a factory can perform jobs at different "levels". The same job may be executed with more or less accuracy, in more or less time, or with a larger or smaller energy consumption [43]. A specific costs value is associated with each job to machine assignment. The MGAP is a variation of the well-known Generalized Assignment Problem (GAP), but the MGAP itself is also used for a variety of problems [43–45]. A GAP is shown to be APX-hard [46], meaning that no polynomial-time approximation scheme exists that can find a solution within some fixed percentage of the optimal solution. The MGAP is formulated as a mathematical model as follows, using the context of our resource management problem:

minimize

$$\sum_{t \in \mathcal{T}} \sum_{e \in \mathcal{E}} \sum_{i \in \mathcal{I}(t)} c_{tei} x_{tei}$$

(3.1)

subject to

$$\sum_{e \in \mathcal{E}} \sum_{i \in \mathcal{I}(t)} x_{tei} = 1 \quad \forall t \in \mathcal{T},$$

(3.2)

$$\sum_{e \in \mathcal{E}} \sum_{i \in \mathcal{I}(t)} R_{\mathcal{I}}(i) x_{tei} \le C_{\mathcal{E}}(e) \quad \forall t \in \mathcal{T}, \tag{3.3}$$

$$x_{tei} \in \{0, 1\} \quad \forall t \in \mathcal{T}, \forall e \in \mathcal{E}, \forall i \in \mathcal{I}(t)$$

The binary decision variable  $x_{tei}$  is defined to be 1 if task t must be executed on element e using implementation i. The objective is to minimize the costs  $c_{tei}$  (Equation 3.1). Alternatively, this objective can be replaced to maximize a profit  $p_{tei}$ . The constraint in Equation 3.2 ensures that precisely one implementation and element combination is selected for each task. In Equation 3.3, the constraint expresses the limited resources available per element; the summed resource requirements of the implementations assigned to element e must not exceed the resource capacity provided by element e.

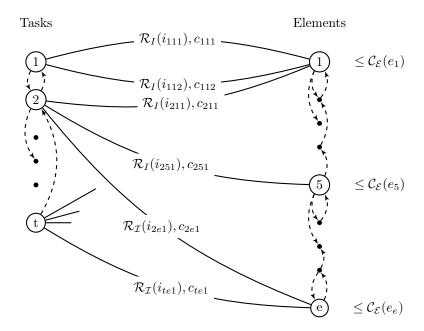

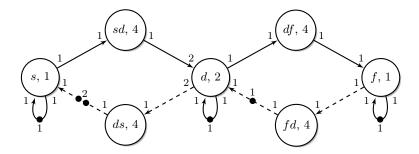

However, this problem formulation can only be considered as our resource management problem when we disregard the spatial factors. The interconnect  $\mathcal{N}$  of a platform  $\mathcal{P}$  introduces a topological relation between members of the set  $\mathcal{E}$ . Likewise, a topological relation exists between tasks within an application. These topological relations not only have an effect on the efficiency of a solution, but on the feasibility of a solution as well. Unfortunately, these relations are difficult to express in an MGAP formulation. Figure 3.1 illustrates the MGAP as a network problem, where arcs between tasks and elements have to be assigned an  $x_{tei} \in \{0, 1\}$ , which indicates whether or not a task-with-implementation to element assignment exists. The dashed arcs within the sets of tasks and elements represent the spatial factors that need to be taken into account as well.

Figure 3.1: The spatial resource management problem.

The MGAP in its original form has a one dimensional representation for size constraints. We use a vector representation for resource requirements and capacities. Vector bin packing is a related class of problems, but bin packing algorithms optimize towards using a minimal amount of bins (elements), which is not necessarily our goal.

Note that this model does not take *scheduling* of resources into account, as in time-sharing. Like in the original description of the MGAP in [42], we consider our problem to be a capacity planning problem. As we assume a composable system, providing sufficient resources implies that we can provide valid schedules to arbitrate over shared resources. Therefore, for simplicity and time constraints we leave scheduling over time out of this thesis.

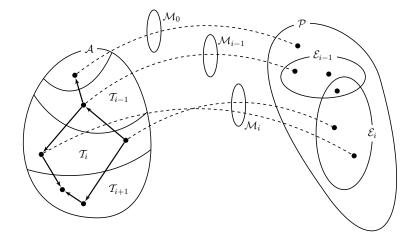

Similar to the hierarchical search approach of [13], we first reduce the search space by choosing for each task the implementation that should be used to realize the application. This removes one dimension of the problem formulation in Equation 3.1-3.3, namely the set of implementations per task  $\mathcal{I}(t)$ . This process is called *binding* and is described in the next section.

### 3.4 Binding phase

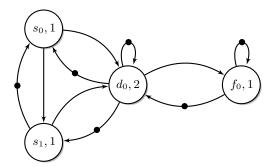

We think of an application as a coherent set of tasks, having no reason to execute only a subset of tasks. For now, we see degradation of an application to a different QoS level as a redefinition of the task graph. So, if the binding phase fails to select an implementation for any task within the application, the application must be rejected. We define a *binding* function to make that choice.

**Definition 6** [Binding] Let  $\mathcal{B}: \mathcal{T} \to \mathcal{I}$  be an injective function that selects for each task  $t \in \mathcal{T}$  in application  $\mathcal{A}$  one of its implementations  $i \in \mathcal{I}(t)$ .

We want to avoid implementations to be selected that cannot be supported by the platform. For a task t, we only consider implementation  $i \in \mathcal{I}(t)$ , if there exists at least one element  $e \in \mathcal{E}$ , that is available for i.

**Definition 7** [Availability] An element e is available, writing av(e, i), for implementation i if the architectural type matches:  $\tau_e = \tau_i$ , and the capacity vector  $C_{\mathcal{E}}(e)$  suffices for the requirement vector  $R_{\mathcal{I}}(i)$ :  $C_{\mathcal{E}}(e) - R_{\mathcal{I}}(i) \geq 0$ .

The availability requirement does not guarantee that enough resources can be allocated to the entire application. We need an extended notion of availability, where a set of elements (the platform) is available for a set of implementations (the application). A binding  $\mathcal{B}$  should guarantee that an *adherent* mapping  $\mathcal{M}$  exists:

**Definition 8** [Mapping, Adherency] Let  $\mathcal{M}: \mathcal{I} \to \mathcal{E}$  be a function that maps an implementation to an element in platform  $\mathcal{P}$ . A mapping  $\mathcal{M}$  is adherent if  $\forall t \in \mathcal{T} | C_{\mathcal{E}}(\mathcal{M}(\mathcal{I}_t)) \geq 0$ .

So, we have to find an assignment from tasks to implementations, while considering the resource vectors. In other words, we want to reduce the MGAP of Equation 3.1-3.3 into a GAP by selecting for every task a single implementation.

An optimal solution in terms of costs requires that each task is assigned an implementation with minimal costs:

$$\forall i \in \mathcal{I}(t) \mid costs(i) \geq costs(\mathcal{B}(t)) \quad \forall t \in \mathcal{T}$$

Referring to Figure 3.1, for each task we remove outgoing arcs that are too expensive to use. After the binding phase, for every task a set of outgoing arcs may remain that effectively point to the same implementation, which can be executed by at least one element.

For reduction of the MGAP, we use a heuristic proposed in [47]. This heuristic uses a cost function, which allows us to be flexible in the optimization direction. The order in which we pick an implementation for each task is based on its desirability. We define the desirability of a task as the difference between the cheapest assignment and the second cheapest assignment of one of its implementations to an element [47]. In other words, if the second best implementation is more expensive, the desirability to map the task increases. The definition of desirability can easily be extended to take additional factors into account, such as the scarcity of specific resources, or the resource requirements of an implementation. Experiments are required to gain better understanding of a good definition.

#### 3.4.1 Implementation

To sustain the adherence of  $\mathcal{M}$ , we virtually assign the chosen implementation to the best fitting element, which is determined in the desirability calculation. The binding choice for the remaining tasks is affected by this assignment, as the available resource capacities in the system are reduced. This guarantees that after this phase (if all tasks are bound), at least one adherent mapping exists if we do not consider the communication restrictions.

Procedure 1 searches for the best possible choice of implementations for the tasks of an application  $\mathcal{A}$ . The heuristic takes into account whether an element is available for an implementation, according to definition 7, and how expensive it is to use that element. Once task t is bound to an implementation, we write  $\mathcal{B}(t)$  to indicate that specific implementation.

The time complexity of the binding procedure is bound by  $O(\mathcal{T} \times \mathcal{I} \times \mathcal{E})$ . One worst-case scenario occurs when the platform is homogeneous in its elements. In heterogeneous systems we can instantly select a pre-arranged subset of platform elements, because each implementation is annotated with an architectural type. However, this does not necessarily give a reduced time complexity, as applications designed for heterogeneous platforms are likely to have more implementations per task than homogeneous applications. The asymptotic time complexity of BindApplication may be reduced to  $O(\mathcal{I} \times \mathcal{E}log\mathcal{E} + \mathcal{I}^2)$ , by sorting for each task, the implementations in decreasing desirability [47]. However, for small numbers this may not be benificial, due to increased memory usage.

**Remark:** If the presented approach is applied to applications consisting only of *elementary tasks*, where precisely one implementation per task is provided, some time could be saved by skipping the binding phase, which includes a check that

# Procedure 1 BindApplication( $\mathcal{A} = \langle \mathcal{T}, \mathcal{C} \rangle$ , $\mathcal{P} = \langle \mathcal{E}, \mathcal{L} \rangle$ ) Ensure: $\mathcal{T}$ ordered by increasing $|\mathcal{I}(t)|$

```

\mathcal{B} \leftarrow \emptyset

repeat

best \leftarrow \langle \emptyset, \emptyset, \emptyset, \infty, \infty \rangle \text{ \{task, implementation, element, fstCost, sndCost\}}

for all t \in \mathcal{T} do

curr \leftarrow \langle \emptyset, \emptyset, \emptyset, \infty, \infty \rangle

5:

for all i \in \mathcal{I}(t) do

for all \{e \in \mathcal{E} \mid av(e,i)\}\ \mathbf{do}

if BindingCost(i, e) < fstCost_{curr} then

curr \leftarrow \langle t, i, e, \text{Cost}(i, e), fstCost_{curr} \rangle

else if BindingCost(i, e) < sndCost then

10:

sndCost_{curr} \leftarrow BindingCost(i, e)

if curr = \emptyset then

fail

if (sndCost_{curr} - fstCost_{curr}) > (sndCost_{best} - fstCost_{best}) then

best \leftarrow curr

15:

\mathcal{B} \leftarrow \mathcal{B} \cup \langle \mathcal{T}_{best}, \mathcal{I}_{best} \rangle

until best = \emptyset

return \mathcal{B}

```

determines if the remaining resource capacities suffice. However, the downside of this approach is that somewhere in the more expensive mapping phase the application may get rejected. This would not hurt the application itself, because it was already going to fail, but it may reversely affect the delay of other queued events.

### 3.5 Mapping phase